Texas Instruments LMK61E07 Handleiding

Texas Instruments Niet gecategoriseerd LMK61E07

Bekijk gratis de handleiding van Texas Instruments LMK61E07 (52 pagina’s), behorend tot de categorie Niet gecategoriseerd. Deze gids werd als nuttig beoordeeld door 2 mensen en kreeg gemiddeld 4.8 sterren uit 6 reviews. Heb je een vraag over Texas Instruments LMK61E07 of wil je andere gebruikers van dit product iets vragen? Stel een vraag

Pagina 1/52

LMK61E07 Ultra-Low Jitter Programmable Oscillator With Internal EEPROM

1 Features

•Ultra-Low Noise, High Performance

–Jitter: 90-fs RMS Typical f

OUT

> 100 MHz on

LMK61E07

–PSRR: –70 dBc, Robust Supply Noise

Immunity on LMK61E07

•Flexible Output Format on LMK61E07

–LVPECL up to 1 GHz

–LVDS up to 900 MHz

–HCSL up to 400 MHz

•Total Frequency Tolerance of ±25 ppm

•System Level Features

–Glitch-Less Frequency Margining: Up to ±1000

ppm From Nominal

–Internal EEPROM: User Configurable Start-Up

Settings

•Other Features

–Device Control: Fast Mode I

2

C up to 1000 kHz

–3.3-V Operating Voltage

–Industrial Temperature Range (–40°C to +85°C)

–7-mm × 5-mm 6-Pin Package

•Default Frequency:

–70.656 MHz

2 Applications

•High-Performance Replacement for Crystal, SAW,

or Silicon-Based Oscillators

•Switches, Routers, Network Line Cards, Base

Band Units (BBU), Servers, Storage/SAN

•Test and Measurement

•Medical Imaging

•FPGA, Processor Attach

•xDSL, Broadcast Video

3 Description

The LMK61E07 family of ultra-low jitter PLLatinum

™

programmable oscillators uses fractional-N frequency

synthesizers with integrated VCOs to generate

commonly used reference clocks. The output on

LMK61E07 can be configured as LVPECL, LVDS,

or HCSL. The device features self-start-up from on-

chip EEPROM to generate a factory-programmed

default output frequency, or the device registers and

EEPROM settings are fully programmable in-system

through an I

2

C serial interface. The device provides

fine and coarse frequency margining control through

an I

2

C serial interface, making it a digitally-controlled

oscillator (DCXO).

The PLL feedback divider can be updated to adjust

the output frequency without spikes or glitches in

steps of <1ppb using a PFD of 12.5 MHz (R

divider=4, doubler disabled) for compatibility with

xDSL requirements, or in steps of <5.2 ppb using a

PFD of 100 MHz (R divider=1, doubler enabled) for

compatibility with broadcast video requirements. The

frequency margining features also facilitate system

design verification tests (DVT), such as standards

compliance and system timing margin testing.

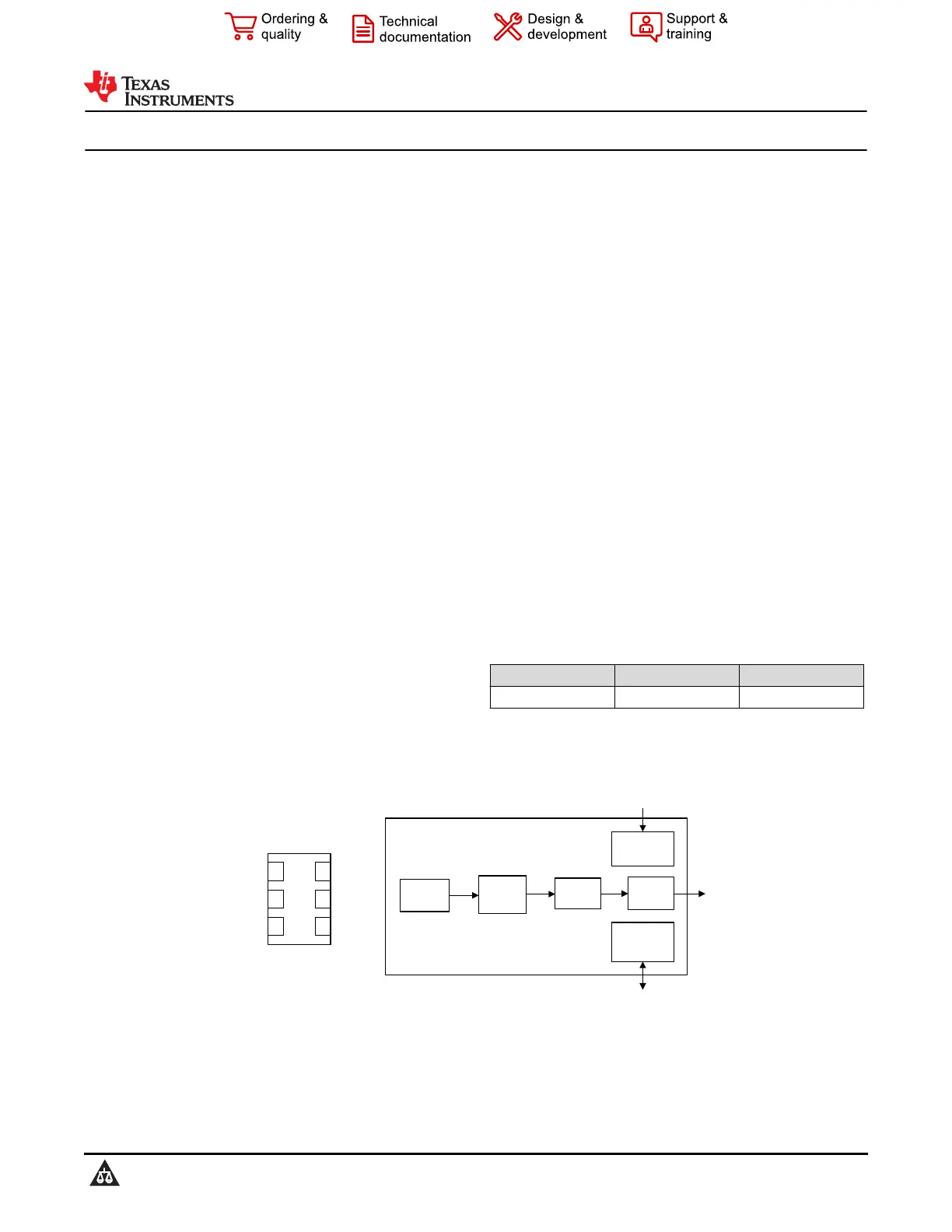

Package Information

(1)

PART NUMBERPACKAGEPACKAGE SIZE

(2)

LMK61E07SIA (QFM, 6)7.00 mm × 5.00 mm

(1)For all available packages, see the orderable addendum at

the end of the data sheet.

(2)The package size (length × width) is a nominal value and

includes pins, where applicable.

SCLOUTN

VDDSDA

GNDOUTP

16

25

43

LMK61E0X

Ultra-high performance oscillator

PLL

Output

Divider

Output

Buffer

Power

Conditioning

Interface

I

2

C/EEPROM

Integrated

Oscillator

Copyright © 2016, Texas Instruments Incorporated

Pinout and Simplified Block Diagram

LMK61E07

SNAS722B – DECEMBER 2017 – REVISED AUGUST 2023

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Product specificaties

| Merk: | Texas Instruments |

| Categorie: | Niet gecategoriseerd |

| Model: | LMK61E07 |

Heb je hulp nodig?

Als je hulp nodig hebt met Texas Instruments LMK61E07 stel dan hieronder een vraag en andere gebruikers zullen je antwoorden

Handleiding Niet gecategoriseerd Texas Instruments

23 April 2026

22 April 2026

21 April 2026

21 April 2026

20 April 2026

14 April 2026

14 April 2026

13 April 2026

13 April 2026

11 April 2026

Handleiding Niet gecategoriseerd

Nieuwste handleidingen voor Niet gecategoriseerd

25 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026

24 April 2026