Microchip TC1321 Handleiding

Microchip Niet gecategoriseerd TC1321

Bekijk gratis de handleiding van Microchip TC1321 (39 pagina’s), behorend tot de categorie Niet gecategoriseerd. Deze gids werd als nuttig beoordeeld door 29 mensen en kreeg gemiddeld 4.9 sterren uit 9 reviews. Heb je een vraag over Microchip TC1321 of wil je andere gebruikers van dit product iets vragen? Stel een vraag

Pagina 1/39

2000 Microchip Technology Inc.Preliminary DS00735A-page 1

INTRODUCTION

This application note describes the implementation of

the PICmicro MSSP module for Master I2C communi-

cations. The Master Synchronous Serial Port (MSSP)

module is the enhanced Synchronous Serial Port

developed by Microchip Technology and is featured on

many of the PICmicro devices. This module provides

for both the 4-mode SPI communications, as well as

Master and Slave I2C communications, in hardware.

For information on the SPITMperipheral implementation

see the PICmicroTM Mid-Range MCU Family Reference

Manual, document DS33023. The MSSP module in I

2C

mode fully implements all Master and Slave functions

(including general call support) and provides interrupts

on START and STOP bits in hardware to determine a

free I2C bus (multi-master function). The MSSP module

implements the standard mode specifications, as well

as 7-bit and 10-bit addressing. Figure 1 depicts a func-

tional block diagram of the I2C Master mode. The appli-

cation code for this I2C example is developed for and

tested on a PIC16F873, but can be ported over to a

PIC17CXXX and PIC18CXXX PICmicro MCU which

features a MSSP module.

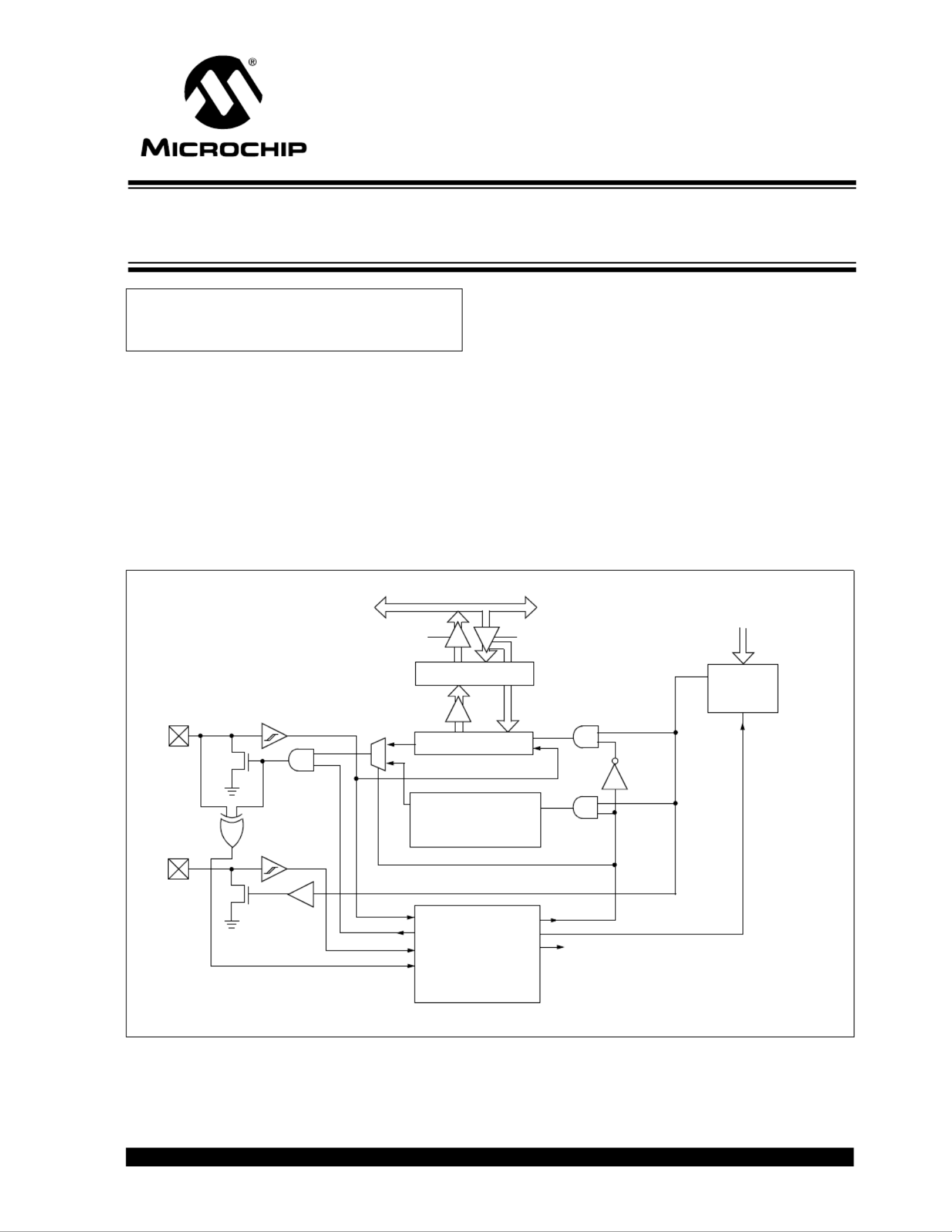

FIGURE 1: I2C MASTER MODE BLOCK DIAGRAM

Author:Richard L. Fischer

Microchip Technology Inc.

Read Write

SSPSR

START bit, STOP bit,

SSPBUF

Internal

Data Bus

Set/Reset, S, P, WCOL (SSPSTAT)

Shift

Clock

MSb LSb

SDA

Acknowledge

Generate

SCL

SCL In

Bus Collision

SDA In

Receive Enable

Clock cntl

Clock Arbitrate/WCOL Detect

(hold off clock source)

SSPADD<6:0>

Baud

Set SSPIF, BCLIF

Reset ACKSTAT, PEN (SSPCON2)

Rate

Generator

SSPM3:SSPM0

START bit detect

STOP bit detect

Write collision detect

Clock Arbitration

State counter for

end of XMIT/RCV

AN735

Using the PICmicro®MSSP Module for Master

I2CTM Communications

Product specificaties

| Merk: | Microchip |

| Categorie: | Niet gecategoriseerd |

| Model: | TC1321 |

Heb je hulp nodig?

Als je hulp nodig hebt met Microchip TC1321 stel dan hieronder een vraag en andere gebruikers zullen je antwoorden

Handleiding Niet gecategoriseerd Microchip

13 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

6 December 2025

5 December 2025

30 November 2025

30 November 2025

Handleiding Niet gecategoriseerd

Nieuwste handleidingen voor Niet gecategoriseerd

24 Januari 2026

24 Januari 2026

24 Januari 2026

24 Januari 2026

24 Januari 2026

24 Januari 2026

24 Januari 2026

23 Januari 2026

23 Januari 2026

23 Januari 2026