Microchip SY89871U Handleiding

Microchip Niet gecategoriseerd SY89871U

Bekijk gratis de handleiding van Microchip SY89871U (13 pagina’s), behorend tot de categorie Niet gecategoriseerd. Deze gids werd als nuttig beoordeeld door 13 mensen en kreeg gemiddeld 4.8 sterren uit 9 reviews. Heb je een vraag over Microchip SY89871U of wil je andere gebruikers van dit product iets vragen? Stel een vraag

Pagina 1/13

SY89871U

2.5GHz Any Diff. In-To-LVPECL

Programmable Clock Divider/Fanout Buffer

w/ Internal Termination

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

Oct. 1, 2013

M9999-010512-F

General Description

The SY89871U is a 2.5V/3.3V LVPECL output precision

clock divider capable of accepting a high-speed differential

clock input (AC or DC-coupled) CML, LVPECL, HSTL or

LVDS clock input signal and dividing down the frequency

using a programmable divider ratio to create a frequency-

locked lower speed version of the input clock (Bank B).

Available divider ratios are 2, 4, 8, and 16. In a typical

622MHz clock system this would provide availability of

311MHz, 115MHz, 77MHz, or 38MHz auxiliary clock

components.

The differential input buffer has a unique internal

termination design that allows access to the termination

network through a VT pin. This feature allows the device to

easily interface to different logic standards. A V

REF-AC

reference is included for AC-coupled applications.

The SY89871U includes two phase-matched output banks.

Bank A (QA) is a frequency-matched copy of the input.

Bank B (QB0, QB1) is a divided down output of the input

frequency. Bank A and Bank B maintain a matched delay

independent of the divider setting.

Data sheets and support documentation can be found on

Micrel’s web site at: www.micrel.com.

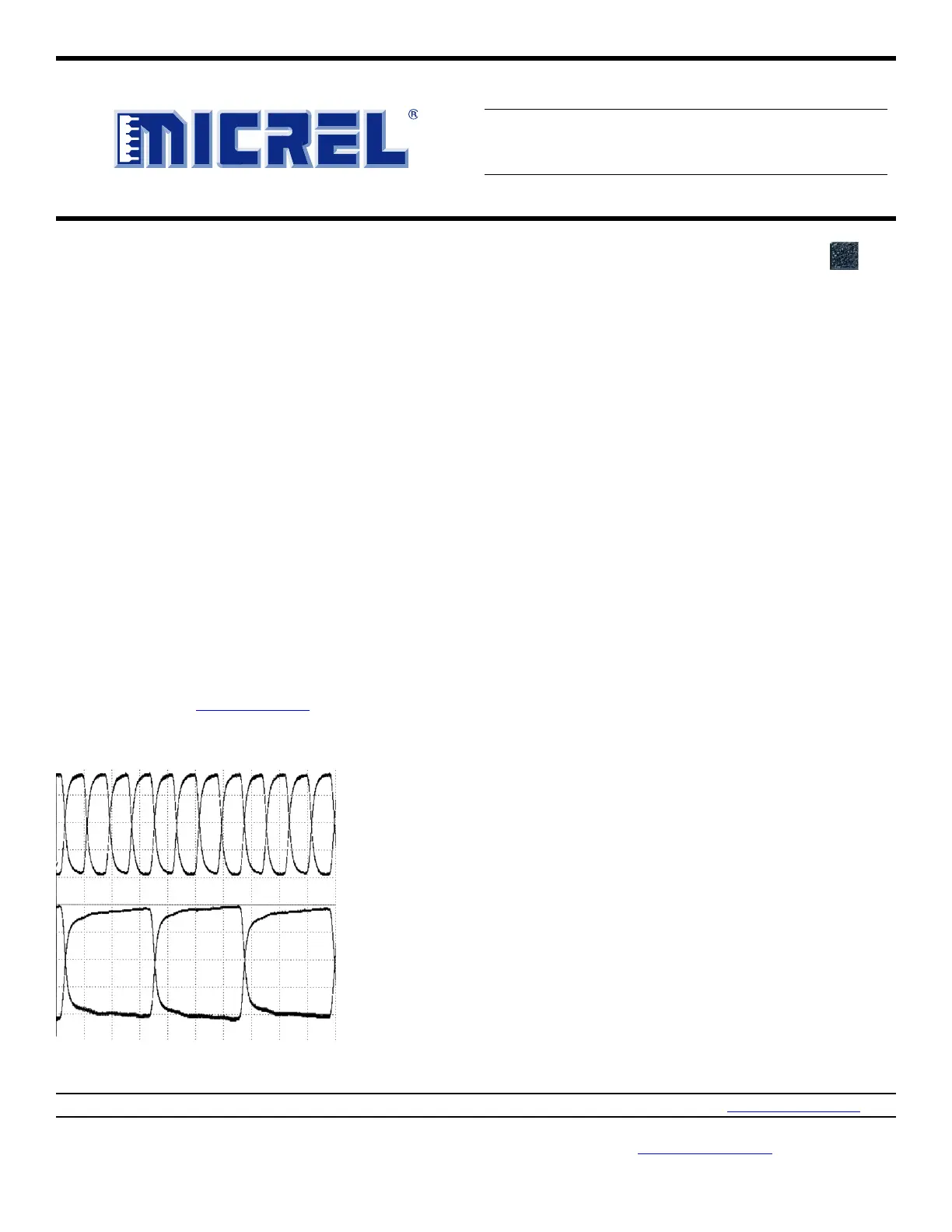

Typical Performance

Precision Edge

®

Features

Two matched-delay outputs:

-Bank A: undivided pass-through (QA)

-Bank B: programmable divide by 2, 4, 8, 16 (QB0,

QB1)

Matched delay: all outputs have matched delay,

independent of divider setting

Guaranteed AC performance:

->2.5GHz f

MAX

-<250ps t

r

/t

f

-<670ps t

pd

(matched delay)

-<15ps within-device skew

Low jitter design

-231fs RMS phase jitter (Typ)

Power supply 3.3V or 2.5V

Unique patent-pending input termination and VT pin for

DC-and AC- coupled inputs: any differential inputs

(LVPECL, LVDS, CML, HSTL)

TTL/CMOS inputs for select and reset

100K EP compatible LVPECL outputs

Parallel programming capability

Wide operating temperature range: -40°C to +85°C

Available in 16-pin (3mm x 3mm) QFN package

Applications

OC-3 to OC-192 SONET/SDH applications

Transponders

Oscillators

SONET/SDH line cards

Precision Edge is a registered trademark of Micrel, Inc

Product specificaties

| Merk: | Microchip |

| Categorie: | Niet gecategoriseerd |

| Model: | SY89871U |

Heb je hulp nodig?

Als je hulp nodig hebt met Microchip SY89871U stel dan hieronder een vraag en andere gebruikers zullen je antwoorden

Handleiding Niet gecategoriseerd Microchip

2 Februari 2026

26 Januari 2026

13 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

6 December 2025

5 December 2025

Handleiding Niet gecategoriseerd

Nieuwste handleidingen voor Niet gecategoriseerd

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026

11 Maart 2026